продукти Категорія

- FM-передавач

- 0-50w 50w-1000w 2kw-10kw 10kw +

- ТВ передавач

- 0-50w 50-1kw 2kw-10kw

- антена FM

- ТВ антени

- антена аксесуар

- кабель з'єднувач розгалужувач харчування еквівалентна навантаження

- RF Transistor

- джерело живлення

- Аудіо обладнання

- DTV Front End обладнання

- система Link

- система STL Система Link Мікрохвильова піч

- FM-радіо

- вимірювач потужності

- інші продукти

- Спеціально для коронавірусу

продукти Теги

Fmuser Сайти

- es.fmuser.net

- it.fmuser.net

- fr.fmuser.net

- de.fmuser.net

- af.fmuser.net -> африкаанс

- sq.fmuser.net -> албанська

- ar.fmuser.net -> арабська

- hy.fmuser.net -> Вірменська

- az.fmuser.net -> азербайджанська

- eu.fmuser.net -> баскська

- be.fmuser.net -> білоруська

- bg.fmuser.net -> болгарська

- ca.fmuser.net -> Каталонська

- zh-CN.fmuser.net -> китайська (спрощена)

- zh-TW.fmuser.net -> китайська (традиційна)

- hr.fmuser.net -> хорватська

- cs.fmuser.net -> чеська

- da.fmuser.net -> данська

- nl.fmuser.net -> Голландська

- et.fmuser.net -> естонська

- tl.fmuser.net -> філіппінська

- fi.fmuser.net -> фінська

- fr.fmuser.net -> французька

- gl.fmuser.net -> галицький

- ka.fmuser.net -> грузинський

- de.fmuser.net -> німецька

- el.fmuser.net -> грецька

- ht.fmuser.net -> гаїтянський креольський

- iw.fmuser.net -> іврит

- hi.fmuser.net -> хінді

- hu.fmuser.net -> Угорська

- is.fmuser.net -> ісландська

- id.fmuser.net -> індонезійська

- ga.fmuser.net -> ірландський

- it.fmuser.net -> італійська

- ja.fmuser.net -> японська

- ko.fmuser.net -> корейська

- lv.fmuser.net -> латиська

- lt.fmuser.net -> литовська

- mk.fmuser.net -> македонська

- ms.fmuser.net -> малайська

- mt.fmuser.net -> мальтійська

- no.fmuser.net -> Норвезька

- fa.fmuser.net -> Перська

- pl.fmuser.net -> польська

- pt.fmuser.net -> португальська

- ro.fmuser.net -> румунська

- ru.fmuser.net -> російська

- sr.fmuser.net -> сербська

- sk.fmuser.net -> словацька

- sl.fmuser.net -> словенська

- es.fmuser.net -> іспанська

- sw.fmuser.net -> суахілі

- sv.fmuser.net -> шведська

- th.fmuser.net -> Тайська

- tr.fmuser.net -> турецька

- uk.fmuser.net -> український

- ur.fmuser.net -> урду

- vi.fmuser.net -> в'єтнамська

- cy.fmuser.net -> валлійська

- yi.fmuser.net -> Ідиш

Що таке Half Adder: Принципова схема та її застосування

Date:2021/10/18 21:55:58 Hits:

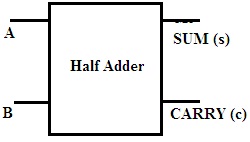

Половина суматора - це тип базової цифрової схеми. Раніше в аналогових схемах виконувались різні операції. Після відкриття цифрової електроніки в ній виконуються подібні операції. Цифрові системи вважаються ефективними та надійними. Серед різноманітних операцій однією з найпомітніших є арифметична. Він включає в себе додавання, віднімання, множення та ділення. Проте вже відомо, що це може бути комп’ютер, будь-який електронний гаджет, наприклад калькулятор, може виконувати математичні операції. Ці операції, що виконуються, складаються з двійкових значень. Це можливо завдяки наявності в ньому певних схем. Ці схеми називаються двійковими суматорами та від’ємниками. Цей тип схем призначений для двійкових кодів, кодів Excess-3 та інших кодів. Подальші двійкові суматори поділяються на два типи. Ними є: напівсуматор і повний суматор.Що таке напівсуматор? Цифрова електронна схема, яка виконує функцію додавання двійкових чисел, визначається як напівсуматор. Процес додавання – це денар, єдина відмінність – вибрана система числення. У двійковій системі нумерації існують лише 0 і 1. Вага числа повністю базується на позиціях двійкових цифр. Серед цих 1 і 0 1 розглядається як найбільша цифра, а 0 — як менша. Структурна схема цього суматора така Напівсуматор Напівсуматор Напівсуматор складається з двох входів і створює два виходи. Вважається найпростішими цифровими схемами. Вхідними даними цієї схеми є біти, до яких слід виконати додавання. Отримані результати є сумою та переносом.

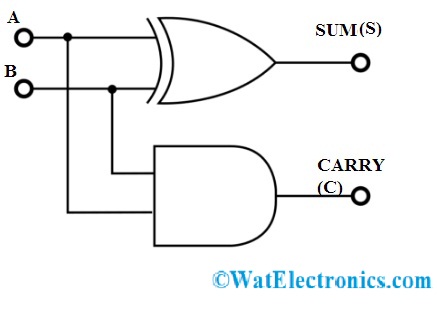

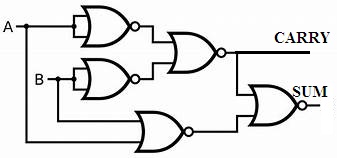

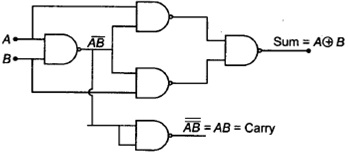

Напівсуматор Напівсуматор Напівсуматор складається з двох входів і створює два виходи. Вважається найпростішими цифровими схемами. Вхідними даними цієї схеми є біти, до яких слід виконати додавання. Отримані результати є сумою та переносом.  Напівсуматор Схема цього суматора складається з двох вентилів. Це ворота І та XOR. Застосовувані входи однакові для обох затворів, присутніх у ланцюзі. Але вихідні дані беруться з кожного входу. Вихід елемента XOR називається SUM, а вихід AND відомий CARRY. Таблиця істини Half Adder. Щоб отримати відношення отриманого виходу до прикладеного входу, можна проаналізувати за допомогою таблиці, відомої як таблиця істинності.

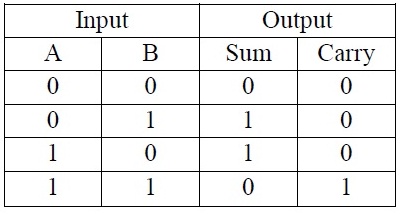

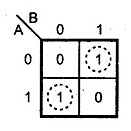

Напівсуматор Схема цього суматора складається з двох вентилів. Це ворота І та XOR. Застосовувані входи однакові для обох затворів, присутніх у ланцюзі. Але вихідні дані беруться з кожного входу. Вихід елемента XOR називається SUM, а вихід AND відомий CARRY. Таблиця істини Half Adder. Щоб отримати відношення отриманого виходу до прикладеного входу, можна проаналізувати за допомогою таблиці, відомої як таблиця істинності. Таблиця істинності половинного суматора З наведеної вище таблиці істинності точки є очевидними наступним чином: якщо A=0, B=0, тобто обидва вхідні дані, дорівнюють 0. Тоді обидва виходи SUM і CARRY дорівнюють 0. Серед двох вхідних даних, застосованих, якщо хтось вхід 1, тоді SUM буде b e1, але CARRY дорівнює 0. Якщо обидва входи дорівнюють 1, то SUM буде дорівнює 0, а CARRY буде дорівнює 1. На основі застосованих входів половина суматора продовжує операцію Рівняння Рівняння для цього типу ланцюгів може бути реалізовано за допомогою концепцій суми добутків (SOP) і добутків суми (POS). Булеве рівняння для цього типу схем визначає відношення між застосованими входами та отриманими виходами. Для визначення рівняння k-карти малюються на основі значень таблиці істинності. Він складається з двох рівнянь, оскільки в ньому використовуються два логічних вентиля. K-карта переносу є

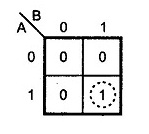

Таблиця істинності половинного суматора З наведеної вище таблиці істинності точки є очевидними наступним чином: якщо A=0, B=0, тобто обидва вхідні дані, дорівнюють 0. Тоді обидва виходи SUM і CARRY дорівнюють 0. Серед двох вхідних даних, застосованих, якщо хтось вхід 1, тоді SUM буде b e1, але CARRY дорівнює 0. Якщо обидва входи дорівнюють 1, то SUM буде дорівнює 0, а CARRY буде дорівнює 1. На основі застосованих входів половина суматора продовжує операцію Рівняння Рівняння для цього типу ланцюгів може бути реалізовано за допомогою концепцій суми добутків (SOP) і добутків суми (POS). Булеве рівняння для цього типу схем визначає відношення між застосованими входами та отриманими виходами. Для визначення рівняння k-карти малюються на основі значень таблиці істинності. Він складається з двох рівнянь, оскільки в ньому використовуються два логічних вентиля. K-карта переносу є  K-Map AND Gate Вихідне рівняння CARRY отримують з вентиля І. C=A.B Булевий вираз для SUM реалізується у формі SOP. Отже, K-карта для SUM є

K-Map AND Gate Вихідне рівняння CARRY отримують з вентиля І. C=A.B Булевий вираз для SUM реалізується у формі SOP. Отже, K-карта для SUM є K-Map для суми (XOR) Визначене рівняння є S= A⊕ B. Застосування цього основного суматора полягають у наведеному нижче. до формування схеми повного додавання.Ці логічні схеми є кращими при розробці калькуляторів. Крім того, це стає серцем цифрової електроніки. Код VHDL Код VHDL для схеми Half Adder islibrary ieee;використовуйте ieee.std_logic_1164.all;entity half_adder isport(a,b: in bit; sum,carry:out bit);end half_adder ;дані архітектури half_adder isbeginsum<= a xor b;переносити <= a та b;кінцеві дані;FAQ1. Що ви маєте на увазі під суматором? Цифрові схеми, єдиною метою яких є виконання додавання, відомі як суматори. Це основні компоненти АЛУ. Суматори працюють на додаток до різних форматів чисел. Вихідними результатами суматорів є сума та перенос.2. Які обмеження половинного суматора? Біт переносу, згенерований з попереднього біта, не може бути доданий, є обмеженням цього суматора. Для виконання додавання для декількох бітів ці схеми не можуть бути кращими. Як реалізувати напівсуматор за допомогою шлюза НІ? Це ще одна Універсальна брама.

K-Map для суми (XOR) Визначене рівняння є S= A⊕ B. Застосування цього основного суматора полягають у наведеному нижче. до формування схеми повного додавання.Ці логічні схеми є кращими при розробці калькуляторів. Крім того, це стає серцем цифрової електроніки. Код VHDL Код VHDL для схеми Half Adder islibrary ieee;використовуйте ieee.std_logic_1164.all;entity half_adder isport(a,b: in bit; sum,carry:out bit);end half_adder ;дані архітектури half_adder isbeginsum<= a xor b;переносити <= a та b;кінцеві дані;FAQ1. Що ви маєте на увазі під суматором? Цифрові схеми, єдиною метою яких є виконання додавання, відомі як суматори. Це основні компоненти АЛУ. Суматори працюють на додаток до різних форматів чисел. Вихідними результатами суматорів є сума та перенос.2. Які обмеження половинного суматора? Біт переносу, згенерований з попереднього біта, не може бути доданий, є обмеженням цього суматора. Для виконання додавання для декількох бітів ці схеми не можуть бути кращими. Як реалізувати напівсуматор за допомогою шлюза НІ? Це ще одна Універсальна брама. Половина додавача за допомогою воріт NOR4. Як реалізувати функцію Half Adder за допомогою NAND Gate? NAND - один із різновидів універсальних воріт. Це вказує на те, що будь-який тип проектування схем можливий за допомогою елементів NAND.

Половина додавача за допомогою воріт NOR4. Як реалізувати функцію Half Adder за допомогою NAND Gate? NAND - один із різновидів універсальних воріт. Це вказує на те, що будь-який тип проектування схем можливий за допомогою елементів NAND. Половина додавача З наведеної вище схеми вихідний сигнал може бути сформований шляхом застосування виходу одного воріт NAND до входу як іншого затвора NAND. Це не що інше, як знайоме з виходом, отриманим із вентиля І. Вихідне рівняння SUM може бути згенеровано, застосувавши вихідні дані початкового елемента NAND разом із окремими входами A та B до наступних вентилів NAND. Нарешті, вихідні дані, отримані цими елементами NAND, знову застосовуються до вентиля. Таким чином, генерується вихід для SUM. Тому основний суматор у цифровій схемі може бути розроблений за допомогою різних логічних вентилів. Але додавання кількох бітів ускладнюється і вважається обмеженням половинного суматора. Чи можете ви описати, яка мікросхема використовується для операції збільшення в будь-яких практичних лічильниках?

Половина додавача З наведеної вище схеми вихідний сигнал може бути сформований шляхом застосування виходу одного воріт NAND до входу як іншого затвора NAND. Це не що інше, як знайоме з виходом, отриманим із вентиля І. Вихідне рівняння SUM може бути згенеровано, застосувавши вихідні дані початкового елемента NAND разом із окремими входами A та B до наступних вентилів NAND. Нарешті, вихідні дані, отримані цими елементами NAND, знову застосовуються до вентиля. Таким чином, генерується вихід для SUM. Тому основний суматор у цифровій схемі може бути розроблений за допомогою різних логічних вентилів. Але додавання кількох бітів ускладнюється і вважається обмеженням половинного суматора. Чи можете ви описати, яка мікросхема використовується для операції збільшення в будь-яких практичних лічильниках?

Залишити повідомлення

список повідомлень

Коментарі Завантаження ...