продукти Категорія

- FM-передавач

- 0-50w 50w-1000w 2kw-10kw 10kw +

- ТВ передавач

- 0-50w 50-1kw 2kw-10kw

- антена FM

- ТВ антени

- антена аксесуар

- кабель з'єднувач розгалужувач харчування еквівалентна навантаження

- RF Transistor

- джерело живлення

- Аудіо обладнання

- DTV Front End обладнання

- система Link

- система STL Система Link Мікрохвильова піч

- FM-радіо

- вимірювач потужності

- інші продукти

- Спеціально для коронавірусу

продукти Теги

Fmuser Сайти

- es.fmuser.net

- it.fmuser.net

- fr.fmuser.net

- de.fmuser.net

- af.fmuser.net -> африкаанс

- sq.fmuser.net -> албанська

- ar.fmuser.net -> арабська

- hy.fmuser.net -> Вірменська

- az.fmuser.net -> азербайджанська

- eu.fmuser.net -> баскська

- be.fmuser.net -> білоруська

- bg.fmuser.net -> болгарська

- ca.fmuser.net -> Каталонська

- zh-CN.fmuser.net -> китайська (спрощена)

- zh-TW.fmuser.net -> китайська (традиційна)

- hr.fmuser.net -> хорватська

- cs.fmuser.net -> чеська

- da.fmuser.net -> данська

- nl.fmuser.net -> Голландська

- et.fmuser.net -> естонська

- tl.fmuser.net -> філіппінська

- fi.fmuser.net -> фінська

- fr.fmuser.net -> французька

- gl.fmuser.net -> галицький

- ka.fmuser.net -> грузинський

- de.fmuser.net -> німецька

- el.fmuser.net -> грецька

- ht.fmuser.net -> гаїтянський креольський

- iw.fmuser.net -> іврит

- hi.fmuser.net -> хінді

- hu.fmuser.net -> Угорська

- is.fmuser.net -> ісландська

- id.fmuser.net -> індонезійська

- ga.fmuser.net -> ірландський

- it.fmuser.net -> італійська

- ja.fmuser.net -> японська

- ko.fmuser.net -> корейська

- lv.fmuser.net -> латиська

- lt.fmuser.net -> литовська

- mk.fmuser.net -> македонська

- ms.fmuser.net -> малайська

- mt.fmuser.net -> мальтійська

- no.fmuser.net -> Норвезька

- fa.fmuser.net -> Перська

- pl.fmuser.net -> польська

- pt.fmuser.net -> португальська

- ro.fmuser.net -> румунська

- ru.fmuser.net -> російська

- sr.fmuser.net -> сербська

- sk.fmuser.net -> словацька

- sl.fmuser.net -> словенська

- es.fmuser.net -> іспанська

- sw.fmuser.net -> суахілі

- sv.fmuser.net -> шведська

- th.fmuser.net -> Тайська

- tr.fmuser.net -> турецька

- uk.fmuser.net -> український

- ur.fmuser.net -> урду

- vi.fmuser.net -> в'єтнамська

- cy.fmuser.net -> валлійська

- yi.fmuser.net -> Ідиш

Що таке Half Subtractor: робота та її застосування, K-MAP, схема з використанням воріт NAND

Date:2021/10/18 21:55:58 Hits:

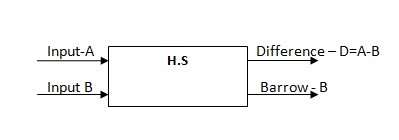

Для обробки інформації, наприклад світла або звуку, від однієї точки до іншої ми можемо використовувати аналогові схеми, подаючи належні входи у вигляді аналогових сигналів. У цьому процесі є ймовірність того, що вхідні аналогові сигнали сприймуть шум, і це може призвести до втрати вихідного сигналу. Це означає, що будь -який вхід, який ми обробляємо на вхідному рівні, не дорівнює вихідному каскаду. Для подолання цих цифрових схем реалізовано. Цифрова схема може бути сконструйована з логічними затворами. Логічні затвори - це електронна схема, яка виконує логічні операції на основі їх входів і видає на вихід лише один біт, або низький (логіка 0 = нульова напруга), або високий (логіка 1 = висока напруга). Комбінаційні схеми можуть бути сконструйовані з кількома логічними затворами. Ці схеми є швидкими та незалежними від часу без зворотного зв'язку між входом і виходом. Комбінаційні схеми корисні для арифметичних та булевих операцій. Найкращі приклади комбінаційних схем включають наполовину суматор, повний суматор, наполовину від’ємник, повний від’ємник, мультиплексори, демультиплексори, кодер та декодер. Що таке половинний від’ємник? використовується для віднімання двох бітів з входу. Тут вихідний від’ємник суто залежить від поточних вхідних даних і не залежить від попередніх етапів. Результати напіввилучення-це різниця та курган. Це подібно до арифметичного віднімання, де в разі, якщо віднімач більший за мінус, ми б взяли позику B = 1, інакше позика залишиться нулем B = 0. Щоб краще зрозуміти це, давайте перейдемо до таблиці правди, наведеної нижче.  Блок-діаграма напіввивісників Таблиця істини Таблиця істини напіввивісників показує вихідні значення відповідно до входів, які застосовуються на вхідних каскадах. Таблиця правди поділена на дві частини. Ліва частина позначається як вхідний каскад, а права частина - як вихідний каскад. У цифрових схемах вхід 0 і вхід 1 вказують на низьку логіку, а логіку на високу. Відповідно до конфігурації, логічний низький означає нульову напругу, логічний високий означає високу напругу (наприклад, 5В, 7В, 12В тощо). Входи Виходи Вхід -AIВхід -BРізниця -DБарроу -B 000010 1001111100 Таблиця правди Пояснення Коли входи A і B дорівнюють нулю, виходи напіввилучувачів D і B також є нульовими. Курган дорівнює нулю Коли вхід A дорівнює нулю, а вхід B високий, то виходи D і B високі з відповідними. Коли обидва входи високі, обидва виходи напіввилучення дорівнюють нулю. З наведеної вище таблиці істинності ми можемо Знайдіть рівняння для Різниці (D) та Кургана (В). Рівняння для Різниці-D: Різниця є високою, коли входи A = 1, B = 1 та A = 0, B = 0. З цього твердження D = AB '+A'B = A⊕B. Відповідно до рівняння D воно позначає Ex-or gate. D = A⊕B Рівняння для Barrow-B: Барро високий лише тоді, коли вхід A низький, а B високий. З цього моменту рівняння для Кургана B буде таким: B = A'BB = A'B З наведених вище різниці та рівнянь Кургана ми можемо спроектувати схему напіввивісників, використовуючи K -MapK -карта MapKarnaugh спрощує вираз булевої алгебри для ланцюга половини віднімача. Це офіційний метод пошуку рівняння булевої алгебри для будь -якої схеми. Давайте вирішимо булеві вирази для схеми напіввилучення за допомогою K-map.K-Map для різниці (D) та Кургана (В)

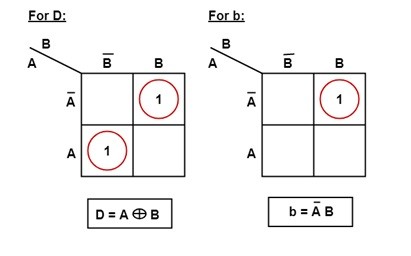

Блок-діаграма напіввивісників Таблиця істини Таблиця істини напіввивісників показує вихідні значення відповідно до входів, які застосовуються на вхідних каскадах. Таблиця правди поділена на дві частини. Ліва частина позначається як вхідний каскад, а права частина - як вихідний каскад. У цифрових схемах вхід 0 і вхід 1 вказують на низьку логіку, а логіку на високу. Відповідно до конфігурації, логічний низький означає нульову напругу, логічний високий означає високу напругу (наприклад, 5В, 7В, 12В тощо). Входи Виходи Вхід -AIВхід -BРізниця -DБарроу -B 000010 1001111100 Таблиця правди Пояснення Коли входи A і B дорівнюють нулю, виходи напіввилучувачів D і B також є нульовими. Курган дорівнює нулю Коли вхід A дорівнює нулю, а вхід B високий, то виходи D і B високі з відповідними. Коли обидва входи високі, обидва виходи напіввилучення дорівнюють нулю. З наведеної вище таблиці істинності ми можемо Знайдіть рівняння для Різниці (D) та Кургана (В). Рівняння для Різниці-D: Різниця є високою, коли входи A = 1, B = 1 та A = 0, B = 0. З цього твердження D = AB '+A'B = A⊕B. Відповідно до рівняння D воно позначає Ex-or gate. D = A⊕B Рівняння для Barrow-B: Барро високий лише тоді, коли вхід A низький, а B високий. З цього моменту рівняння для Кургана B буде таким: B = A'BB = A'B З наведених вище різниці та рівнянь Кургана ми можемо спроектувати схему напіввивісників, використовуючи K -MapK -карта MapKarnaugh спрощує вираз булевої алгебри для ланцюга половини віднімача. Це офіційний метод пошуку рівняння булевої алгебри для будь -якої схеми. Давайте вирішимо булеві вирази для схеми напіввилучення за допомогою K-map.K-Map для різниці (D) та Кургана (В) K-карта для різниці (D) і Барроу (B) Відповідно до K-карти, перший імпликант-A'B, а другий-AB'. = A'B+AB'Тоді, D = A⊕B. Це рівняння просто вказує на ворота Ex-OR. Щоб знайти спрощений булевий вираз для кургана B, нам потрібно виконати той самий процес, якого ми дотримувалися для Різниці D. Тому B = A'B. NOR ворота називаються універсальними. Тут ворота NAND називаються універсальними, тому що ми можемо спроектувати будь -який тип цифрової схеми з використанням n комбінацій чисел NAND. Завдяки цій спеціальності ворота NAND називають універсальними. Тепер ми проектуємо схему напіввилучення за допомогою воріт NAND.

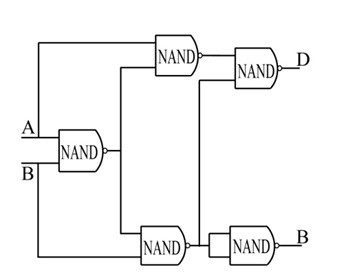

K-карта для різниці (D) і Барроу (B) Відповідно до K-карти, перший імпликант-A'B, а другий-AB'. = A'B+AB'Тоді, D = A⊕B. Це рівняння просто вказує на ворота Ex-OR. Щоб знайти спрощений булевий вираз для кургана B, нам потрібно виконати той самий процес, якого ми дотримувалися для Різниці D. Тому B = A'B. NOR ворота називаються універсальними. Тут ворота NAND називаються універсальними, тому що ми можемо спроектувати будь -який тип цифрової схеми з використанням n комбінацій чисел NAND. Завдяки цій спеціальності ворота NAND називають універсальними. Тепер ми проектуємо схему напіввилучення за допомогою воріт NAND. Ми можемо спроектувати схему напіввилучення з п'ятьма затворами NAND. Розглянемо A і B як входи для першого ступеня шлюзу NAND, його вихід знову з'єднаний як один вхід до другого затвора NAND а також третій затвор NAND. Відповідно до своїх входів, він дає вихід, а на завершальному етапі від воріт NAND різницевий вихід D та вихід B кургана будуть на їх виході. Остаточне різницеве значення D різниці D = A ⊕B і рівняння кургана B як B = A'B. Використовуючи різну комбінацію воріт NAND для побудови напіввід’ємника, кінцеві рівняння різниці та кургана будуть лише D = A⊕B та B = A'B. Половини від’ємника Існують різні застосування цих від’ємників. Практично їх просто аналізувати. Деякі з них перераховані наступним чином. Щоб відняти числа, розташовані в найменшій позиції у стовпцях, ці від’ємники є кращими. Арифметично -логічна одиниця (ALU), присутня в процесорі, надає перевагу цій одиниці для віднімання. Щоб мінімізувати спотворення звуку На основі операції, що вимагається, половинний від'ємник має можливість збільшувати або зменшувати кількість операторів. Половини від'ємників використовуються в підсилювачі. Під час передачі звукових сигналів вони використовуються для уникнення спотворень. Таким чином, це все про Схема половинного від'ємника. В умовах реального часу віднімання декількох чисел бітів неможливо зробити за допомогою напіввіднімачів. Цей недолік можна подолати, використовуючи повний від’ємник.

Ми можемо спроектувати схему напіввилучення з п'ятьма затворами NAND. Розглянемо A і B як входи для першого ступеня шлюзу NAND, його вихід знову з'єднаний як один вхід до другого затвора NAND а також третій затвор NAND. Відповідно до своїх входів, він дає вихід, а на завершальному етапі від воріт NAND різницевий вихід D та вихід B кургана будуть на їх виході. Остаточне різницеве значення D різниці D = A ⊕B і рівняння кургана B як B = A'B. Використовуючи різну комбінацію воріт NAND для побудови напіввід’ємника, кінцеві рівняння різниці та кургана будуть лише D = A⊕B та B = A'B. Половини від’ємника Існують різні застосування цих від’ємників. Практично їх просто аналізувати. Деякі з них перераховані наступним чином. Щоб відняти числа, розташовані в найменшій позиції у стовпцях, ці від’ємники є кращими. Арифметично -логічна одиниця (ALU), присутня в процесорі, надає перевагу цій одиниці для віднімання. Щоб мінімізувати спотворення звуку На основі операції, що вимагається, половинний від'ємник має можливість збільшувати або зменшувати кількість операторів. Половини від'ємників використовуються в підсилювачі. Під час передачі звукових сигналів вони використовуються для уникнення спотворень. Таким чином, це все про Схема половинного від'ємника. В умовах реального часу віднімання декількох чисел бітів неможливо зробити за допомогою напіввіднімачів. Цей недолік можна подолати, використовуючи повний від’ємник.

Залишити повідомлення

список повідомлень

Коментарі Завантаження ...